# JOINT ADVANCED STRIKE TECHNOLOGY PROGRAM

## **AVIONICS ARCHITECTURE DEFINITION**

**VERSION 1.0**

9 August 1994

Lt Col Chuck Pinney, JAST Avionics Lead 1215 Jefferson Davis Highway, Suite 406 Arlington, VA 22202

phone: 703-602-7390 ext. 6625 e-mail: pinneyc@ntrprs.jast.mil

**Technical Contacts:**

Reed Morgan Wright Laboratory Avionics Directorate WPAFB, OH 45433 513-255-4709 morgandr@aa.wpafb.af.mil Ralph Lachenmaier Code 505B Naval Air Warfare Center Warminster, PA 18974 215-441-1634 lachenmaier@nadc.navy.mil

#### **EXECUTIVE SUMMARY**

This document contains Version 1.0 of the Joint Advanced Strike Technology (JAST) Avionics Architecture Definition. It will be used in the development and demonstration of a set of matured technologies and modular avionics functions to be used in Engineering and Manufacturing Development (EMD) of next-generation strike weapons systems for the Navy, Marine Corps, Air Force and allied nations. The purpose of the Architecture Definition is twofold: (1) to provide a basis for planning risk reduction demonstrations, analyses, and modeling efforts, and (2) when mature and complete, to establish a framework for the consistent application of avionics building blocks to meet the needs of specific platforms. The architecture describes digital hardware modules and components, the system software definition and its design and support environment, the system interconnects, the sensor functions, the electrical power distribution approach, and mechanical aspects of the avionics including packaging and thermal management.

A systematic process has been put in place to develop and update the Architecture Definition. A select group of avionics experts has been assembled from Navy and Air Force organizations to form an Integrated Product Team (IPT). Using the best information available on current and projected avionics technology and on the goals of the JAST program, with especially heavy emphasis on affordability, the IPT developed Version 0.0 of the Architecture Definition as a vehicle to initiate a dialog with the avionics community in both government and industry. The initial version was widely circulated, and extensive written and oral critiques were received. An architecture review board, with extensive industry participation, performed an issue definition and adjudication process with the goal of bringing Version 0.0 to the level of maturity needed to support near term JAST avionics development efforts.

As a result of this adjudication process, the original document has been extensively revised, and a new direction for the maturation and demonstration of JAST avionics concepts has been adopted. The process will be event-driven, with need dates for closure of the remaining avionics issues chosen on the basis of availability of information and of the timing of follow-on activities which depend on decision outcomes. The basic features of the Version 0.0 architecture were maintained, but the revised document is more open in that a wider range of alternative solutions for individual areas of the architecture will be tracked and evaluated up to the point where a decision is needed. In many areas, a leading candidate and a set of tracked alternatives have been identified. Every attempt has been made to incorporate the full spectrum of valid contenders for such areas as sensor integration, system interconnect, and power distribution, recognizing that fiscal and schedule constraints will set limits on the scope of investigation of alternative approaches. Furthermore, the JAST Program will maintain a continuing interaction with industry and government as the Architecture Definition matures and as issues are resolved to ensure that all pertinent information is incorporated and that industry is fully prepared for the start of EMD. Facilitating this interaction are: expansion of the Avionics IPT membership to include the weapons system concept contractors and industry associations representatives, normal interchange as part of JAST contractual efforts, the creation of an Avionics electronic bulletin board, and periodic "Industry Day" briefings.

This Architecture Definition supports the JAST Avionics concept development/demonstration program whose goal is to establish the basis for development in EMD of low risk, affordable avionics suites for a variety of strike weapon systems. This effort is tightly coupled to the overall JAST weapon system concept development and demonstration. Among the products which the JAST program will make available to EMD program managers are:

- Results of a series of risk reduction demonstrations (RRDs) and Integrated Technology Demonstrations focused on specific technical and cost issues;

- Results produced by an end-to-end virtual avionics prototype, including pilot-in-the-loop simulations, to validate the operational suitability of avionics suites with a range of functions and capabilities. The VAP supports the development of the overall JAST weapon system concept. It reflects functional allocations

from the Strategy-to-Task-to-Technology process and provides information on the capabilities and costs of alternative avionics concepts to the weapon system engineering process;

- A set of modular avionics functions, with their associated implementing technologies, which have been reduced to an acceptable level of risk through analysis and demonstration and characterized in terms of cost, performance, and technical maturity for use in EMD. These "building blocks" will include digital information processing hardware and software, a software design and support environment, an information transfer network structure and protocols, sensors and sensor management functions, cockpit/avionics integration, weapons integration and targeting, electrical power distribution, and mechanical aspects of avionics, including packaging and thermal management techniques; and

- An avionics architecture standard which will serve as a framework for tailoring an avionics suite which employs these building blocks and is optimized in terms of cost and performance for any given platform. The architecture will be based on a form/fit/interface (F<sup>2</sup>I) approach and will include design rules and implementing standards which comprise a set of "building codes" for avionics suites based on JAST avionics building blocks.

The point of departure for the JAST Avionics Architecture Definition was the Joint Integrated Avionics Working Group (JIAWG)/F-22 Advanced Avionics Architecture. This starting point was chosen because it represents the most recent avionics development in DoD. A description of the F-22 avionics suite is given in Annex A. That baseline has been enhanced in the JAST architecture to take advantage of technology and system concepts which have emerged in recent years. The JAST baseline is thus appropriate for an aircraft which will enter EMD in FY 2000 with an Initial Operational Capability date of 2010. The JAST baseline also supports the primary JAST goal of reducing life cycle cost (LCC) and of supporting a variety of weapon system platforms with a common inventory of technologies and modular functional capabilities.

Key features of the JAST avionics architecture, as described in detail in this document, include the following:

- Emphasis on affordability, open systems adaptability, scalability, incorporation of commercial technology and products, technology independence and growth provisions, and support for high levels of reliability, maintainability, supportability, and deployability;

- Use of an advanced unified digital interconnect scheme;

- Infrastructure which provides efficient, reliable power distribution, environmentally tolerant packaging, reliable connection for electrical and optical signals, and cooling for high intrinsic reliability of electronic devices;

- Extensive support for built-in test and fault isolation, reconfigurability for failure management, and maintenance support;

- Use of an advanced information architecture, supported by a partitioned software architecture, open system-compliant processing hardware, and a mature software engineering environment and methodology;

- Support for commonality, interoperability, and affordable long-term insertion of emerging technology;

- · Integrated sensor functions, including sensor management and multifunction apertures; and

- Advanced information management, including fusion of on-board and off-board data sources, support for target recognition and precision targeting, and support for high levels of aircrew situational awareness.

This Architecture Definition is the basic member of a family of documents which collectively describe the JAST avionics architecture and the program through which the avionics concept will be developed and demonstrated. The companion documents, which should be used in conjunction with the definition document to obtain a complete picture of JAST avionics activities, are:

- The JAST Avionics Concept Development/Demonstration Plan (JACDDP) which describes the sequence of studies, demonstrations, and simulation and modeling efforts that will provide the data to refine and validate the avionics concept and the architecture;

- An Issues/Decision/Rationale Document which contains a full description of issues, alternatives, decisions, rationale and a record of issue closures;

- An Annex Document with descriptions of F-22 avionics and other programs which provide support to JAST; and

- An Appendix Document which describes significant technology, standardization, and other programs which have contributed to the enhancement of the F-22 baseline in defining the initial JAST architecture.

Updated versions of the JAST Avionics Architecture Definition will be published with the completion of significant milestones, when essential data becomes available, and as event-driven decisions are made. The release of next version is planned for 3QFY96, although an interim update may be necessary. Comments and relevant information are welcome from all knowledgeable parties. The dialog which has been established, and which proved effective in migrating Version 0.0 to Version 1.0, will be maintained through all available channels, including widespread electronic distribution of this and related documents. Table 0-1 summarizes the primary areas now under consideration, including the corresponding approach in the F-22 point of departure, the leading and other alternatives, and the date by which a decision is required (D-Date) to support subsequent activities.

The Architecture IPT wishes to express gratitude to the industry and government participants whose extensive work and cooperative attitude were essential to the timely completion of this document.

Table 0-1 JAST Avionics Architecture Candidate Standards ("Building Blocks")

| F-22 (JIAWG)                                           |                                             | JAST                                   |                         |

|--------------------------------------------------------|---------------------------------------------|----------------------------------------|-------------------------|

| Point of Departure<br>MECHANICA                        | Leading Alternative MECHANICAL              | Tracked Alternatives                   | D-Date                  |

| <ul> <li>SEM-E Format</li> </ul>                       | <ul> <li>SEM-E Format</li> </ul>            | • Larger, Ease of Manufac.             | •Mar 97                 |

| <ul> <li>Liquid Flow Thru Cooling</li> </ul>           | • Liquid Flow Thru Cooling                  | • Conduct., Air Flow Thru              | •Mar 97                 |

| • Conduct. Cooling (VMS)                               | <ul> <li>Conduct. Cooling (VMS)</li> </ul>  | <ul> <li>Liquid Flow Thru</li> </ul>   | •Mar 97                 |

| Bendix Connector                                       | <ul> <li>Bendix Connector</li> </ul>        | <ul> <li>Smaller Connectors</li> </ul> | •Mar 97                 |

| ELECTRICAL                                             | ELECTRICAL                                  |                                        |                         |

| •270V Prime Power                                      | <ul> <li>270V Prime Power</li> </ul>        | • 115/230V 400/800-1600 H              | HaMar 97                |

| •5V Power Thru Bkplane                                 | • 48 V Power Thru Bkplane                   | • 28/270V, (5V, 3.3V, +-15\            | √ <mark>)</mark> Mar 97 |

| INTERCONNECTS (N/W)                                    |                                             |                                        |                         |

| <ul> <li>Interconnects/ buses</li> </ul>               | <ul> <li>Unified Network Protoco</li> </ul> | l • Multiple Interconnects             | •Mar 96                 |

| (Pi, TM, DFN, HSDB) & FOTR                             | (SCI)                                       | (F-22, Fibre Chan., ATM)               |                         |

| PROCESSORS                                             | PROCESSORS                                  |                                        |                         |

| <ul><li>Many Processor Types</li><li>SENSORS</li></ul> | • Few Processor Types <b>SENSORS</b>        | App. Specific Processors               | •Mar 97                 |

| <ul> <li>Dedicated Apertures</li> </ul>                | <ul> <li>Integrated Apertures</li> </ul>    | • Wideband Rx, Narrow Tx               | •Dec 97                 |

| <ul> <li>Dedicated RF Electronics</li> </ul>           | <ul><li>Time-Shared RF Mod.</li></ul>       | • F-22 RF Electronics                  | •Dec 97                 |

| SOFTWARE                                               | SOFTWARE                                    |                                        |                         |

| • Op Sys, Sys Mg(Propr.)                               | <ul> <li>POSIX (Commercial)</li> </ul>      | • F-22,Commercial Dev.                 | •Mar 96                 |

| •Ada 83                                                | • Ada 9X                                    | •C/C++                                 | •Mar 96                 |

| <ul> <li>Graphics I/F (Custom)</li> </ul>              | • X-11/Motif                                | • X-Windows, GKS, PHIGS                | •Mar 9                  |

## TABLE OF CONTENTS

| EXECUTIVE SUMMARY                                                   | i  |

|---------------------------------------------------------------------|----|

| 1.0 INTRODUCTION                                                    | 1  |

|                                                                     |    |

| 2.0 JAST AVIONICS ARCHITECTURE GUIDELINES                           | 4  |

| 2.1 Affordability                                                   | 4  |

| 2.2 SCALABILITY                                                     | 4  |

| 2.3 OPEN SYSTEM ADAPTABILITY                                        | 4  |

| 2.4 Commercial Technology                                           |    |

| 2.5 RELIABILITY AND SUPPORTABILITY                                  |    |

| 2.6 Technology Independence and Growth                              |    |

| 2.7 DATA RATE AND THROUGHPUT GUIDELINES                             |    |

| 2.7.1 Application Definitions                                       |    |

| 3.0 JAST ARCHITECTURE                                               | 8  |

| 3.1 Use of Commercial Technology                                    |    |

| 3.2 STANDARDS ONLY AT THE INTERFACES                                |    |

| 3.3 ADVANCED UNIFIED DIGITAL INTERCONNECT                           |    |

| 3.3.1 Characteristics Required of A Unified Interconnect Protocol   |    |

| 3.3.2 Using a Unified Network for the Test Maintenance Function     |    |

| 3.4.1 Aircraft Primary Power                                        |    |

| 3.4.2 Backplane Power                                               |    |

| 3.5 MODULE COOLING                                                  |    |

| 3.6 MODULE FORM FACTOR, MECHANICAL, AND CONNECTOR                   |    |

| 3.7 ADVANCED STORES MANAGEMENT/WEAPON SYSTEM INTERFACE              |    |

| 3.8 ADVANCED SYSTEM INSTRUMENTATION AND SOFTWARE DEBUG FACILITY     |    |

| 3.9 ADVANCED PROCESSORS                                             | 19 |

| 4.0 SOFTWARE DESIGN, DEVELOPMENT, AND SUPPORT                       | 21 |

| 4.1 Introduction                                                    | 21 |

| 4.2 Ada Programming Language                                        | 21 |

| 4.3 PARTITIONED AVIONICS SOFTWARE ARCHITECTURE                      |    |

| 4.3.1 Mission Software                                              |    |

| 4.3.2 System/Support Software                                       |    |

| 4.4 MISSION SOFTWARE ARCHITECTURE                                   |    |

| 4.5 SOFTWARE DEVELOPMENT PROCESS                                    | 25 |

| 4.6 SOFTWARE DEVELOPMENT ENVIRONMENT                                |    |

| 4.8 Information Architecture Concept                                |    |

| 5.0 SUBSYSTEM ARCHITECTURES                                         |    |

| 5.1 Integrated RF Sensor System                                     |    |

| 5.1 INTEGRATED RF SENSOR SYSTEM                                     |    |

| 5.2.1 Federated Aperture Configuration; Current Technology Baseline |    |

| 5.2.2 Enhanced Aperture Configuration                               |    |

| 5.3 Integrated Electro-Optical Sensors                              |    |

| 5.3.1 Processing Requirements                                       |    |

| 5.4 Off-Board Assets                                                |    |

| 6.0 LIST OF LEADING CANDIDATE STANDARDS                             | 35 |

####

## APPENDICES1

- A. The IEEE SCI-- An Approach For A Unified Avionics Network

- B. PAVE PACE Description

- C. Advanced Avionics Subsystems & Technologies (AAS&T)/Next Generation Computer Resources (NGCR)

- D. Supportability Guidelines

## ANNEXES<sup>1,2</sup>

- A. JAST Avionics Architecture Point of Departure/F-22 Description

- B. Advanced Shared Aperture Program Overview

#### JAST AVIONICS ARCHITECTURE DEFINITION ISSUES/DECISIONS/RATIONALE DOCUMENT

| 1.0  | Purpose                         | 1 |

|------|---------------------------------|---|

| 2.0  | Scope                           | 1 |

|      | Issues/Decisions/Rationale      |   |

| 3.1  | Commercial Off-the-Shelf (COTS) | 1 |

| 3.2  | Interconnects                   |   |

| 3.3. | Electrical Power                | 2 |

| 3.4  | Packaging                       | 3 |

| 3.5  | Stores Management System        | 4 |

| 3.6  | Processors                      |   |

| 3.7  | Software                        | 4 |

| 3.8  | Sensors                         | 7 |

|      |                                 |   |

#### Notes:

- 1. Appendices, Annexes, and the Issues/Decision/Rationale Documents are published under separate covers.

- 2. Annexes are unchanged per Industry/Government review. Comments received in the annexes have been reflected in Version 1.0 of the Avionics Architecture Definition Document.

#### 1.0 Introduction

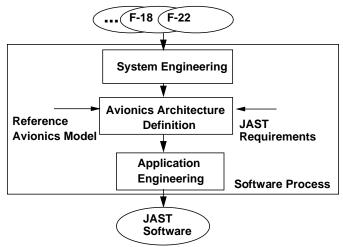

The JAST Program is chartered to facilitate evolution of fully developed and validated operational requirements, proven operational concepts, and mature demonstrated technologies to support successful development and production of next generation strike weapon systems for the U.S. Air Force, Navy, Marine Corps, and our allies. To support this charter, the Avionics Integrated Product Team (IPT) has the responsibility to develop and demonstrate an affordable avionics "building block" of matured technologies ready for low-risk transition for a 1 October 1999 entry into the Engineering and Manufacturing Development (EMD) phase for a next generation strike weapon system. Essential to this process is the early formation of an infrastructure—the JAST avionics architecture—upon which the avionics building block will evolve. This document, the Avionics Architecture Definition, describes the architecture and facilitates avionics evolution by: (1) providing a basis for planning risk reduction demonstrations, analyses, and modeling efforts, and (2) when mature and complete, establishing a framework for the consistent application of avionics building blocks to meet the needs of specific The architecture—the "building codes" of avionics—describes digital hardware modules and components, the system software definition and its design and support environment, the system interconnects, the sensor functions, the electrical power distribution approach, and mechanical aspects of the avionics including packaging and thermal management. This section describes the process used to develop the architecture, how it ties into the overall JAST Avionics efforts, the salient points of its current form, and future plans for its evolution.

A systematic process has been used to develop and update the Architecture Definition. An integrated product team (IPT) of Air Force and Navy engineers and scientists developed the JAST avionics baseline using the F-22 EMD avionics as a point of departure (largely because it represents the most recent approach to avionics development in the DoD), and incorporating appropriate enhancements offered by newer technologies. The criteria by which these enhancements "earned their way onto the architecture" were applicability to JAST and its range of strike aircraft requirements, lower life cycle costs, and a maturation path which would ensure a low risk transition of that technology to EMD. Version 0.0 described this baseline and was released on 5 June 1994 to industry, government, and academia for review and comment (over 100 organizations reviewed the document). The Architecture IPT, expanded in membership to include weapon system concept contractors and industry associations representatives, then convened an adjudication review board over a four-week period. This IPT, along with several additional invited architecture experts in the field of avionics, reviewed and discussed the over 650 comments received. This version reflects the results of that review process. The comments were wide and varied. Many influenced the standards; some even influenced the architecture definition strategy itself.

For example, in response to a consistent comment that the Version 0.0 standards prematurely drove to a point solution which had not "earned its way onto the architecture," the Architecture IPT refocused the Definition process to follow a more event-driven strategy. Based on the JAST goals of affordable avionics capable of meeting a range of strike requirements in the 2010 to 2040 timeframe, the state of technology and it projections for the future, and the Avionics maturation plan, the board identified the viable candidates for each standard, where applicable, and determined the "need date" to reach a downselect decision. This procedure not only permits near-term design trade flexibility and avoids premature "lock-in" of standards which may later become inappropriate, but it also bounds the architecture framework and ensures that the architecture evolves with the appropriate definition to support the avionics building block and the overall weapon system concept development. [The decision dates are tied to specific events identified in the JAST Avionics concept development and demonstration plan. The plan, published under separate cover, offers the latest description of the sequence of studies, demonstrations, and simulation and modeling efforts that will provide the data to refine and validate the avionics concept and the architecture.]

Because of schedule and resources constraints, the review board divided the standards candidates into leading and tracked alternatives. The leading candidates, based on the data available to date, best complied with the JAST architecture guidelines (see Section 2). The alternative candidates offer both a feasible competitor as well as a potential fall-back solution to the leading candidate. All candidates, including the leading candidate, must earn

their way onto the architecture as a result of life cycle cost analysis, and demonstrated results. During the period leading up to the downselect decision dates, a combination of data review, trade studies, and demonstrations will be used to determine the appropriate standard to use. Concurrent to these evaluations will be avionics risk reduction, concept development, and demonstration activities supporting the weapon system concept and a 1 Oct 99 Milestone II decision. Thus, the process used to develop the architecture both drives and responds to the other Avionics activities.

This Architecture Definition supports the overall JAST Avionics effort: it is the basic member of a family of documents which collectively describe the JAST avionics architecture and the program through which the avionics concept will be developed and demonstrated. The companion documents (each published under separate cover), which should be used in conjunction with the definition document to obtain a complete picture of JAST avionics activities, are:

- The JAST Concept Development and Demonstration Plan which describes the sequence of studies, demonstrations, and simulation and modeling efforts that will provide the data to refine and validate the avionics concept and the architecture;

- An Issues/Decision/Rationale Document which contains a full description of issues, alternatives, decisions, and decision rationale and a record of issue closures—in essence, a traceability document for decisions made today which affect activities later in the program;

- An Annex Document describing the F-22 avionics and Airborne Shared Aperture Program—useful information that provide both support and reference for JAST avionics concept development; and

- An Appendix Document which describes significant technology, standardization, and other programs which have contributed to the enhancement of the F-22 baseline in defining the initial JAST architecture.

In its current form, the Architecture Definition contains the following salient points or features:

- Emphasis on affordability, open systems adaptability, scalability, incorporation of commercial technology and products, technology independence and growth provisions, and support for high levels of reliability, maintainability, supportability, and deployability;

- Use of an advanced unified digital interconnect scheme;

- Infrastructure which provides efficient, reliable power distribution, environmentally tolerant packaging, reliable connection for electrical and optical signals, and cooling for high intrinsic reliability of electronic devices;

- Extensive support for built-in test and fault isolation, reconfigurability for failure management, and maintenance support;

- Use of an advanced information architecture, supported by a partitioned software architecture, open system-compliant processing hardware, and a mature software engineering environment and methodology;

- Support for commonality, interoperability, and affordable long-term insertion of emerging technology;

- · Integrated sensor functions, including sensor management and multifunction apertures; and

- Advanced information management, including fusion of on-board and off-board data sources, support for target recognition and precision targeting, and support for high levels of aircrew situational awareness.

The JAST avionics architecture described in this document assumes a very broad definition of strike avionics characteristics. Specific numbers in terms of operations per second, instructions per second, bits per second, weight, power allocations, source lines of code, etc., are not specified. Instead, this document provides some estimates necessary to scale and bound the problem. This document assumes an open system architecture that will allow the addition and deletion of functionality using a "plug and play" scenario for hardware with unambiguous software interfaces. Proprietary information is minimized and any number of vendors could provide hardware and software that meets the interface standards. Table 0-1 (see Executive Summary) summarizes the primary issues now under consideration, including the corresponding approach in the F-22 point of departure, the leading and other alternatives, and the date by which a decision is required (D-Date) to support subsequent activities.

While Version 1.0 represents the current definition of the JAST avionics architecture, the Architecture Definition is a living document which will evolve over the course of the JACDDP. Various concepts and trade studies for JAST avionics are ongoing and new studies will soon be underway. The mix of on-board and off-board assets that will provide the warfighter with effective mission performance at the lowest cost will be determined and demonstrated over the next few years. These efforts will refine the architecture definition and the avionics contribution to the weapon system concept. Updated versions of the JAST Avionics Architecture Definition will be published with the completion of significant milestones, when essential data becomes available, and as event-driven decisions are made. The release of next version is planned for 3QFY96, although a interim update may be necessary.

Comments and relevant information to Version 1.0 from all knowledgeable parties are welcome. The dialog which has been established, and which proved effective in migrating Version 0.0 to Version 1.0, will be maintained through all available channels, including widespread electronic distribution of this and related documents.

The Architecture IPT wishes to express gratitude to the industry and government participants whose extensive work and cooperative attitude were essential to the timely completion of this document.

[Note: Version 1.0 differs in format from Version 0.0 in three ways. First, changes in the text and tables are indicated by "change bars" in the right-hand margin. Second, several sections now show the applicable standard, the leading and alternative candidates, and the associated downselect decision date. Finally, under separate cover, the "Issues/Decision/Rationale Document" provides a composite picture of the various issues addressed in Version 0.0 and the accompanying industry/government comments. The adjudication board's decisions and supporting rationale provide both insight and a historical trace of the architecture definition process.]

#### 2.0 JAST Avionics Architecture Guidelines

The Architecture IPT has established the following guidelines for establishing the architecture standards and identifying viable candidates.

## 2.1 Affordability

Affordability is of primary importance to the JAST. Therefore the JAST avionics architecture must be predominantly driven by cost considerations. The avionics architecture should seek to reduce life cycle costs, especially development costs. Affordability constraints require the architecture to support an open system concept, insertion and use of commercial and openly available military technology/standards, and the reuse of software.

#### 2.2 Scalability

The JAST avionics architecture should be guided by the need to adapt to a wide range of strike mission requirements and systems. The architecture must be able to handle future growth in requirements and different needs among the Navy, Air Force, and Marines. A JAST scalable architecture should emphasize the partitioning and modularity of software and hardware. In addition to modularity, the interconnect system, the power distribution system, and the cooling system must be able to handle increased loads to meet whatever needs arise. Overall, the avionics architecture must meet the need for additional functionality with incremental improvements without disrupting existing performance or compromising needed capability.

## 2.3 Open System Adaptability

The JAST avionics should promote the use of an open architecture to allow modules built by different vendors to work together and to promote increased competition at the module level. Development costs can be reduced by not relying on proprietary hardware and software. By publishing open system module standards early in the development process vendors are encouraged to seek opportunities and develop modules for areas where they feel they have a competitive edge. Open systems with well-defined standard interfaces create an environment where vendors can compete for specific modules without competing for the entire system.

#### 2.4 Commercial Technology

The JAST architecture should rely heavily on commercial software and hardware technology to control costs. The use of commercial technology reduces the avionics development costs and offers an upgrade path to newer technology as it is developed by commercial industry. This provides a means of attaining the maximum in available performance not only at development time, but also over the life of the aircraft. Commercial software and design environments allow avionics designers and implementors to use more mature (higher quality) tools during the JAST development phase. However, the harsh environment and restraints on weight and volume found in tactical aircraft place restrictions on the amount of commercial technology which can be used.

#### 2.5 Reliability and Supportability

Reliability and supportability are significant features of the JAST avionics. They are significant contributors to overall aircraft availability in both peacetime and wartime. Aircraft availability impacts the total number of aircraft required, and hence the cost, for a given combat capability. Aircraft unavailable because of malfunctioning avionics make no contribution to the war fighting capability.

Avionics reliability and availability have a large impact on the size (and hence the cost) of the maintenance "tail". If the aircraft has a high reliability and availability, it may be possible to fight the early days of a war without avionics maintenance capability. This may be particularly important for ground based aircraft such as the AF uses, because maintenance personnel and equipment must often be deployed to newly established remote bases.

The JAST avionics should continue to operate in the presence of data/timing errors, failed hardware modules, and software errors. Accordingly, fault-tolerance and integrated diagnostics are important considerations in meeting the reliability and supportability constraints. However, the amount of redundant avionics components which can be economically carried to provide this capability must be carefully evaluated. Too little redundancy will result in an aircraft with low availability. Too much redundancy will result in an overly large and costly aircraft. Moreover, the possible need to fight the early days of a war without a maintenance capability can affect the required level of redundancy.

Fault tolerance and integrated diagnostics support in commercial module designs may not be as extensive as that desired for military applications. Joint Test Action Group (JTAG) and other test provisions are becoming more prevalent, but commercial vendors do not generally dedicate sufficient resources to test and diagnostics needed to meet military requirements. This limitation will be considered when making decisions about the use of commercial components.

The JAST avionics architecture should support a reduced maintenance concept. Repair level analysis and LCC analyses will be performed to determine the most cost effective maintenance concept that meets user requirements. As a minimum, the architecture should support two-level maintenance and in some cases, one level maintenance or throw away modules.

The JAST avionics architecture maintainability requirements will be based on the most stringent Navy, Air Force, and Marine requirements. In the case of the Navy, for example, the carrier has limited flight deck space in which any repairs or maintenance can be performed. In addition, it is a harsh environment for opening up aircraft. Carrier decks host high intensity electro-magnetic fields that can potentially damage the exposed electronics. Moreover, spills from fluids onto a steel deck are of concern to the Navy.

A paperless data flow, continuous from on-aircraft fault data storage to organizational repair data to depot level module repair should be encouraged. There should be a standardized electronic format established for the transfer of maintenance and BIT data. This will aid in the reduction of can-not-duplicate (CND) discrepancies.

Other advanced reliability and supportability concepts should be considered for the JAST avionics architecture. For example, paperless technical orders, on-module storage of module status and fault data, and integrated diagnostics, among others, can influence the affordability and LCC of JAST avionics.

#### 2.6 Technology Independence and Growth

The JAST avionics architecture should minimize the reliance on specific technology implementations. The architecture should emphasize well defined interfaces, communication protocols, and software modularization that allows it to evolve over time. Target hardware and software should be upgradable without causing a need for a massive redesign. In addition, the number and need for specialized processors should be minimized by the architecture.

## 2.7 Data Rate and Throughput Guidelines

Table 2.7-1 contains the projected data rate and throughput for various electro-optical (EO), radar, electronic warfare (EW), and communication, navigation, and identification (CNI) applications. These data have been provided by various government sources, along with contractor inputs during the Version 1.0 adjudication process. Overall, the projected data rate for a JAST 2010 EO system is 120 - 700 Mbits/sec per channel and 15 - 25 GOPS for throughput. A JAST 2010 radar system is projected to require an estimated data rate of 200 - 800 Mbits/sec per channel and a throughput of 2 - 15 GOPS. A JAST 2010 EW suite is projected to require an estimated data rate per channel of 0.05 - 2.0 Gbits/sec and 1 -3 GOPS throughput (exclusive of the EO fraction carried above). CNI throughput is projected at 30 - 50 GOPS, but most of this is typically done by specialized preprocessors.

The numbers given in the Table 2.7-1 assume that the given function will be included in the aircraft sensor or processing suite. This may not be the case. Off-board sensors may replace some of the functions listed. Therefore, the numbers given are only an estimate of what may be required if the function/sensor listed is on-board.

The data rates given in the table 2.7-1 are for unbuffered data rates. The ADAS data rate is an aggregate data rate of multiple sensors.

The processing throughput requirements are based on the "to be delivered" throughput as opposed to the "specified processor" throughput. This is an important distinction since the specified processor throughput will be higher than the "to be delivered" throughput based on the processor efficiency. For example, if a processor is capable of achieving 50% throughput for a given application and the required delivered throughput is 9 GFLOPS, then the specified processor throughput will need to be at least 18 GFLOPS. Experiences have been that it is possible to have processor efficiencies less than 50%, therefore, the required specified throughputs are driven up even more drastically than the example.

**Table 2.7-1 Data Rate And Throughput Projections**

| Application (Year 2010)        | Application (Year 2010) Data Rate Projection Throughput Projection |                          |  |

|--------------------------------|--------------------------------------------------------------------|--------------------------|--|

|                                | (per channel)                                                      | (includes preprocessing) |  |

| IRST                           | 120 - 200 Mbits/sec                                                | 4 - 10 GOPS              |  |

| FLIR                           | 120 - 160 Mbits/sec                                                | 3 - 10 GOPS              |  |

| ADAS                           |                                                                    |                          |  |

| SIT Awareness                  | 150 - 700 Mbits/sec                                                | 4 - 10 GOPS              |  |

| Navigation                     | 150 - 700 Mbits/sec                                                | 1 - 2 GOPS               |  |

| Threat Warning                 | 150 - 700 Mbits/sec                                                | 1 - 4 GOPS               |  |

| RGHPRF                         | 280 Mbits/sec                                                      |                          |  |

| ASLC + RGHPRF                  | 280 Mbit/sec                                                       | 2-15 GOPS                |  |

| SAR                            | 200-800 Mbits                                                      |                          |  |

| EW-RF (RWR/ESM)                | 1 -2 Gbits/sec                                                     | 0.5 - 2.0 GOPS           |  |

| EW-EO (Missile Warning)        | SEE ADAS ABOVE                                                     | SEE ADAS ABOVE           |  |

| EW-C3 (Special Receiver)       | 200 - 400 Mbits/sec                                                | 0.5 - 1.0 GOPS           |  |

| EW-EO (Laser Warning)          | 50 - 100 Mbits/sec                                                 | 50 - 100 MIPS            |  |

| Total EO                       |                                                                    | 15-25 GOPS               |  |

| Total Radar                    |                                                                    | 2-15 GOPS                |  |

| Total EW suite                 |                                                                    | 5 - 11 GOPS              |  |

| Total CNI suite (WBDL+GPS+IFF) | TBD                                                                | 30 - 50 GOPS*            |  |

<sup>\*</sup> Normally done by specialized preprocessors

#### 2.7.1 Application Definitions

<u>Infra-Red Search and Track (IRST):</u> EO function used in an offensive situation and includes both spatial and temporal processing. Will be either a stand-alone function or a simultaneous function with either Automatic Target Recognition (ATR) or an Advanced Distributed Aperture System (ADAS).

<u>Forward Looking Infra-Red (FLIR)</u>: EO function used for targeting. Will be either a stand-alone function or a simultaneous function with either ATR or ADAS.

Advanced Distributed Aperture System (ADAS): EO function used for pilot night vision situation awareness for either: (a) IR threat warning for short-range ground to air missiles or (b) for defensive IRST against long-range air-to-air targets or ground-to-air missiles. The ADAS is a multi-sensor configuration in which sensors are distributed on the skin of the aircraft. The data rate given in the table is an aggregate of the total sensor data rate.

Range-Gated High Pulse Repetition Frequency (RGHPRF): Radar function used for an all aspect (nose and tail) air-to-air waveform.

<u>Adaptive Side Lobe Cancellation (ASLC):</u> Radar function used for the cancellation of side lobes. This function would be used simultaneously with the RGHPRF.

Synthetic Aperture Radar (SAR): Air-to-ground radar function used for image ground targets.

Electronic Warfare - Radar Frequency (EW-RF): Radar warning receiver (RWR) function and electronic support measures (ESM) function for electronic countermeasures will be combined with the data rate and throughput projections given for a 500 Mhz instantaneous bandwidth channel with multiple high-speed analog to digital converters. Additional instantaneous bandwidth requires additional channels.

<u>Electronic Warfare (EW-EO & C3):</u> Passive missile warning, laser warning, and special receiver functions are all aspect (multi-apertures) and include multi-spectral, spatial, and temporal processing. Missile warning will be either a stand-alone function or combined with other EO sensors given above.

<u>Communication, Navigation, and Identification (CNI) Suite</u>: CNI functions include wideband data link, GPS, and IFF. The throughput projection includes preprocessing.

#### 3.0 JAST Architecture

The JAST architecture is based on the definition of overall system concepts and identification of interfaces and "building codes". These building codes include the specification of digital interfaces, module mechanical format (including cooling and module size), power, backplane, and other interconnects, and software using the guidelines outlined in Section 2.0. Advances in technology gained through the Air Force PAVE PACE program, the Navy Advanced Avionics Subsystems and Technologies (AAST), and the Next Generation Computer Resources (NGCR) programs, as well as others, have been leveraged to reduce risks and LCC in defining this architecture.

The key features of this architecture are as follows:

- Commercial technology will be exploited to the maximum extent possible consistent with tactical aircraft requirements.

- A unified avionics network protocol is proposed to replace numerous types of aircraft-internal networks. This advanced network is expected to result in cost and weight savings due to decreased module input/output (I/O) pin count, fewer gateway modules, and the capability to locate processing resources anywhere in the aircraft, as well as supporting simplified control software.

- A robust architecture allows for cost savings through the sharing of resources and the flexible use of off-board assets to allow an austere platform to be used for a variety of missions.

- Leveraging the module mechanical and cooling technology from the F-22 is proposed to provide low risk approach, to reduce costs through economies of scale and to provide retrofit for the F-22.

- Software interfaces across the application to operating system boundaries are proposed to use POSIX/Ada 9X bindings in such a way as to break hardware/software dependencies. As a result, software should be more easily reused within and across weapon systems, resulting in cost savings.

- Integrated RF support electronics are proposed as a major cost savings through resource sharing. Further, the unified network approach allows the extensive use of BIT and system reconfiguration at the module level for both digital and RF hardware. A savings in maintenance and manpower costs is expected to result.

- Shared RF apertures are proposed to the extent which they reduce cost for the capability needed. Since the JAST program anticipates the extensive use of off-board sensors, the need for sharing apertures across functions may be minimized.

- An integrated EO subsystem is proposed to achieve affordability, mission needs, and reduce aircraft signature. Again, the extensive use of off-board sensors may reduce the need for integrating EO subsystems.

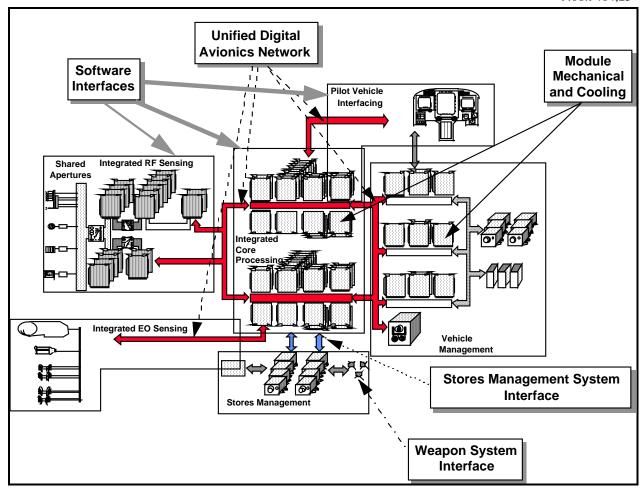

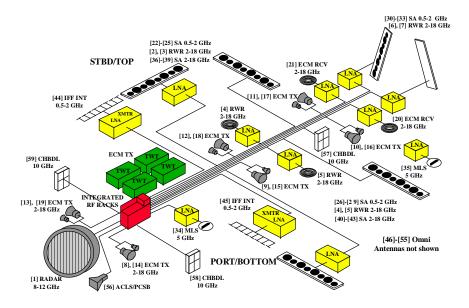

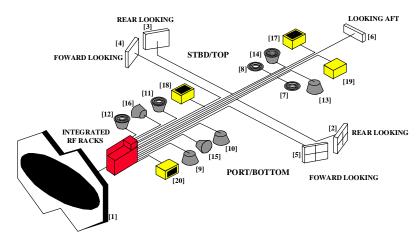

The JAST architecture, as shown in Figure 3.0-1, is based on the PAVE PACE architecture which has been identified as an appropriate evolution of the F-22 point-of-departure architecture. An overview of the PAVE PACE architecture is provided in Appendix B. The architecture consists of an integrated core processing subsystem, an integrated RF sensing subsystem, shared RF apertures, an integrated EO sensing subsystem, a stores management system, a vehicle management system, and a pilot vehicle interface, as well as the interconnects among them. The unified digital avionics network provides the interconnect between the integrated core processor, the sensing functions, the vehicle management system (VMS), and the pilot vehicle interface.

Figure 3.1 JAST Advanced Architecture Showing Interface Standardization Areas

#### 3.1 Use of Commercial Technology

A prime tenet of the JAST architecture is to reduce costs by using commercial technology to the greatest extent possible. Use of commercial technology is most possible and most desirable in the digital area where the commercial computer industry is making giant strides yearly. In the analog area, while commercial industry is still moving rapidly, many of the developments are not as directly applicable to the military as in the digital area. For example, in the area of RF circuits, the DoD is finding it necessary to fund the Microwave/Millimeter-wave Monolithic Integrated Circuit (MIMIC) program while in the area of digital circuits development is moving ahead without DoD funding. In the area of sensor and aperture development, the DoD is the leader. As a result, the commercial sector is leveraging DoD technology more than DoD leverages commercial technology. However, there are still instances in the analog circuitry area and the sensor area where commercial and military technology overlap and commercial technology or manufacturing can be leveraged.

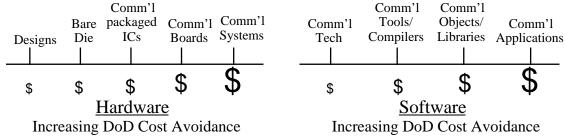

Figure 3.1-1 shows a spectrum of use of commercial digital hardware and software technology in military systems. While some military systems (such as the Navy Tactical Advanced Computer used on ships) have been successful in working at the right hand side of the hardware and software spectra shown below, tactical aircraft have traditionally been closer to the left hand side. Digital hardware environments have required high temperature Integrated Circuits (ICs) in hermetic packages and mounted on boards able to withstand extreme vibration. However, JAST is seeking to move more toward the right of the spectrum.

Figure 3.1-1. Spectrum of Using Commercial Technology

In particular, the JAST architecture provides for leveraging commercial designs for computer data processing CPUs, for signal processing central processing units (CPUs), for memories, and for support circuitry. It also allows for using "mil-spec" versions of commercial computers including parallel processors. This permits support software and operating systems to be moved with relatively little modification directly from commercial systems to the JAST architecture. The areas where modification may be necessary are real time support, fault tolerance, security, and built-in-test (BIT). The recent DoD Directive to utilize commercial products to the maximum extent practicable will result in up-front studies to determine the extent to which the technology can be affordable used.

#### 3.2 Standards Only At The Interfaces

Another basic tenet of the JAST architecture is that standards are specified only at the module interface level. This is sometimes termed a form, fit, interface  $(F^2I)$  approach rather than the form, fit, function, interface  $(F^3I)$  approach which was proposed for JIAWG avionics. The  $F^2I$  approach has been used by the Navy NGCR program. With it no attempt is made to standardize what functions a module performs nor how it performs them. It is left to the module developer to determine what goes into the module as a function of life cycle cost considerations. The use of a standard application program interface (API) and programming in a high order language such as Ada may alleviate the need to specify a particular instruction set architecture. However, these benefits need to be weighed against the supportability issues incurred with multiple ISAs. It is recommended that the decision of whether or not to specify a particular ISA, or family of processors, be left to the EMD teams and that the decision be one of affordability.

#### 3.3 Advanced Unified Digital Interconnect

| Standard:          | Interconnect                                                                     |

|--------------------|----------------------------------------------------------------------------------|

| Goal:              | A unified digital interconnect protocol covering all digital interconnects       |

| Leading Candidate: | IEEE Std 1596-1992, IEEE Standard for Scalable Coherent Interface (to be used un |

|                    | SCI/RT is available)                                                             |

| Other Candidates:  | F-22 interconnects, Fibre Channel, ATM, Custom interconnects                     |

| Decision Date:     | March 1996                                                                       |

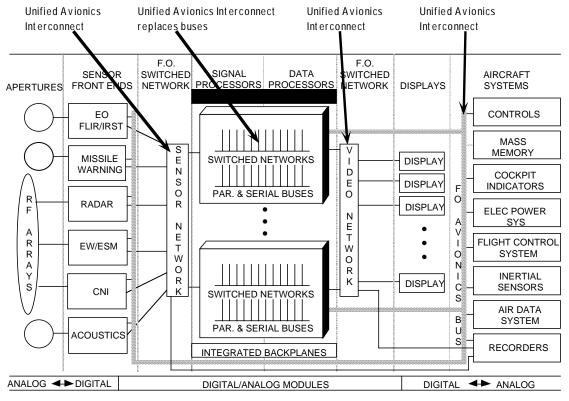

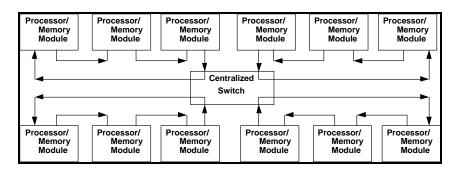

An advanced unified digital avionics interconnect protocol is planned for the JAST architecture. Advances in technology since the mid 1980s have produced new commercial interconnects with speeds an order of magnitude higher than those currently used in our most advanced aircraft--although these networks are yet to be proven in tactical aircraft. The speed and flexibility of these new interconnects opens the opportunity for reducing JAST avionics costs by allowing a single interconnect protocol to replace most or all of the interconnects in our current advanced aircraft. Figure 3.3-1 shows a typical integrated avionics system with a single unified interconnect performing the functions of a variety of, what have been, separate interconnects. For example, in the case of an F-22 like architecture the unified interconnect could replace the Parallel Interconnect (PI)-Bus, the Data Network (DN), the Test and Maintenance (TM)-Bus, the High Speed Data Bus (HSDB), and the sensor/ video/ inter-rack connection.

Figure 3.3-1

An Avionics System with a Single Unified Network Protocol Replacing Several Different Current Interconnects

## 3.3.1 Characteristics Required of A Unified Interconnect Protocol

The general characteristics sought in a unified interconnect protocol are that it have high speed, low latency, support for both message passing and shared memory computing paradigms, scalability from small to

large systems, support for a serial, or low pin-count parallel, instantiation, support for both distributed and centralized switches, support for both electrical and optical physical layers, relative insensitivity to distance, fault tolerance, support for real time computing, and low cost.

High throughput is needed for high bandwidth sensors, and the bandwidth needed to interconnect sensors will increase as analog to digital (A/D) converters increase in speed. Work is going forward on all-digital RF systems in the lower frequency range allowing the carrier frequency to be sampled directly (with extremely fast A/D converters). Experiments are being conducted with optical and other technologies applied to A/D converters which will result in sampling in the giga samples per second range and network requirements in the giga-byte per second range.

High throughput is also needed for inter-processor communications. For example, shared memory systems require extremely high bandwidth (and low latency) interconnects. Shared memory type processors hold promise for applying commercial parallel processor and supercomputer technology to computationally intensive avionics problems. Supercomputer technology has the advantage that its applications software is quite transportable and easily scales upward allowing it to be moved to newer technology hardware with minimal change. Applying this technology would also allow leveraging of the large commercial investment in parallel processor and supercomputer software. In addition, high throughput interconnects simplify even message passing systems by eliminating the necessity for programmers to optimize software to reduce message traffic.

Low latency is needed particularly by shared memory systems, but also by message passing systems which use the same network for command and control as for data flow--as is required for the unified interconnect protocol. In shared memory applications, even cache coherent ones, very high speed (300 Mhz and up) processors may be stalled for hundreds of cycles if the network has high latency. In message passing systems, high latency interconnects often result in very low efficiency parallel processors. Recent experiments in commercial message passing parallel processor systems have demonstrated that even moderately high latency interconnects can have a devastating effect on processor efficiency.

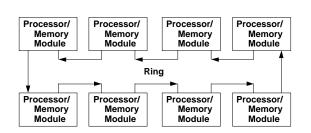

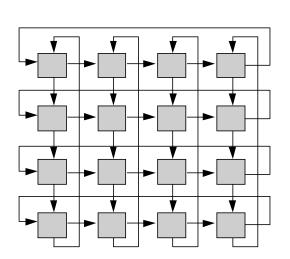

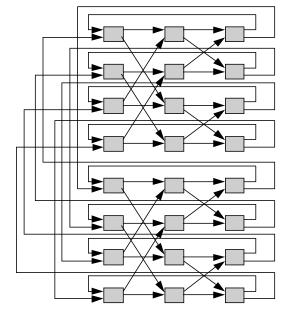

Scalability of the interconnect is needed to allow addition of the numerous new functions which will be required through the thirty years, or more, life of the aircraft. It is also needed to allow insertion of new higher performance technology which will undoubtedly be developed during this thirty plus years. A scalable interconnect protocol provides a low cost interconnection for low performance systems while growing in bandwidth for high performance systems. Serial, or low pin count parallel, interconnects are required to reduce the complexity of the backplane and to reduce the vulnerability of the system to connector contact failure. Both distributed and centralized switch support is needed to accommodate the wide range of design space required to provide the optimum solution for different computational functions. Figures 3.3.2-1 through 3.3.2-5 show some of the many different designs which the interconnect needs to support.

Electrical and optical physical layers are needed to meet the range of requirements a unified network must support. Electrical implementations are cheapest (at this point in time) and generally suitable for module to module communications inside a rack. Optical interconnects are immune to EMI and can travel long distances. Rack to rack and sensor to rack interconnects are likely to be optical. Distance insensitivity in the interconnect allows computing devices to be placed in the aircraft wherever it is most convenient for maintenance access, for weight balance, or for other reasons. It also allows the same interconnect to be used for sensor-to-rack and rack-to-rack interconnect as well as module-to-module interconnect. The general level of fault tolerance required of the interconnect is that failures should have a high probability of detection and that no single failure should take down the entire interconnect (in some cases it may be acceptable to lose a section of the interconnect). Generally this requires a redundant interconnect or some form of error correction.

A real time capability is needed to allow high priority command and control data to be delivered in a timely fashion, even when mixed with large amounts of low priority data. This can be done by using non-shared interconnects (e.g. centralized switch), lightly loaded interconnects, or by some form of scheduling.

Cost effectiveness involves much more than the cost of the interconnect. It includes cost avoidance by being highly scalable for future upgrades as well as cost avoidance by supporting easy-to-program computing paradigms. It also includes cost avoidance (including the aircraft structure multiplier) by eliminating bridge and interface modules.

The leading candidate for the unified interconnect protocol is the IEEE Scalable Coherent Interface (SCI) and its derivative SCI/Real Time (SCI/RT). SCI is an established IEEE commercial standard (IEEE 1596) with integrated circuits (ICs) now available off-the-shelf. SCI/RT is an enhancement to SCI mainly to improve its real time and fault tolerance capabilities. A draft version of SCI/RT standard is now available from the IEEE with some changes still being made. SCI can provide a near-term unified interconnect protocol with a goal of shifting to SCI/RT.

#### 3.3.2 Using a Unified Network for the Test Maintenance Function

Performing the test-maintenance function on a unified network requires attention to some special considerations. To perform the module test function requires a "back door" access to resolve the ambiguous test case where a module does not respond to a query and it is not known if the module or the interconnect failed. Use of dual interconnects on a module can satisfy this need as well as provide fault tolerance when an interconnect fails.

Processor/ Memory Module

Processor/ Memory Memory Module

Processor/ Memory Module

Processor/ Memory Module

Figure 3.3.2-1 Basic Ring

Figure 3.3.2-2 Central Switch Two Party Rings

Figure 3.3.2-3 Rings Interconnected by a Switch

Figure 3.3.2-4 Distributed Switch, Toroidal Mesh Fault Tolerant

Figure 3.3.2-5 Distributed Switch, Wrapped Butterfly -- Fault Tolerant

#### 3.4 Advanced Electrical Power Description

## 3.4.1 Aircraft Primary Power

| Standard:          | Primary Power                                                                  |

|--------------------|--------------------------------------------------------------------------------|

| Goal:              | To choose the optimal primary power for the aircraft and avionics.             |

| Leading Candidate: | F-22-270 VDC                                                                   |

| Other Candidates:  | 115/230V@400 Hz (most current aircraft), 115/230@800-1600 Hz (newer airliners) |

| Decision Date:     | Mar 97                                                                         |

The JAST avionics architecture power distribution system will be supplied by the aircraft's primary electrical power system which will provide either 270 volt DC power, 115/230 volt, 3 phase, 400 Hz power, or 115/230 volt, 3 phase, 800-1600 Hz power. The leading candidate is 270 volt DC, because of extensive F-22 power trade studies, which examined efficiency, cost, weight, volume, and spectral purity requirements of the aircraft. However, additional trades will be made due to the Navy carrier requirements and existing carrier support equipment. In the case of electronically scanned arrays, a 270 VDC to consumption voltage single-stage converter is the preferred concept.

#### 3.4.2 Backplane Power

| Ctondond  | Doolenlana Doyyar |

|-----------|-------------------|

| Standard: | Backplane Power   |

|           | T                 |

| Goal:              | To choose the optimal backplane power for the avionics.                           |

|--------------------|-----------------------------------------------------------------------------------|

| Leading Candidate: | 48 VDC as described in IEEE 896.5, Standard for Futurebus+, Profile M (Military), |

|                    | Section 6.4.1 Profile Power                                                       |

| Other Candidates:  | 28 VDC, 270 VDC, (5 V, 3.3 V, ±15 VDC (analog))                                   |

| Decision Date:     | Mar 97                                                                            |

For integrated racks that may support both digital and analog circuitry, the goal is to use a single backplane distribution voltage of 48 VDC. Small on-module converters would then be used to convert the 48 V to 5 V, 3.3 V, 2.5 V, and lower voltages as needed for digital circuitry. On-module converters would also be used to convert the 48 V to  $\pm 15$  V or other voltages needed for analog circuitry. This creates a two-stage power conversion system for the integrated racks as opposed to the single-stage conversion used for the sensors. The first stage conversion is done inside the rack by 270 V to 48 V converter modules. The second stage conversion is done on-module by a very small 48 V-to-consumption voltage converter.

The motivation for two-stage conversion and distribution of 48 V through the backplane is to reduce the backplane amperage required for low voltage but high power consumption modules. With the very high density of electronics now being achieved, modules in the power consumption range of 200 Watts are anticipated. In addition, low voltage ICs are being developed for lap top computers and other applications. Currently 3.3 V parts are beginning to be used. In the near future, 2.5 V parts are anticipated. In the more distant future, 1.5 V or 1.25 V ICs are expected. Combining a 200 Watt module with 2.5 V circuitry requires 80 amperes of consumption current. This is too much amperage to be handled by either the backplane connector or the backplane itself. Moreover, because of high frequency switching of on-module circuitry, most amperage is carried on the surface of the conductor. This "skin effect" phenomenon requires that large numbers of power and ground planes be used in the backplane to control the noise. The result is a very heavy and expensive backplane. Increasing the backplane voltage to 48 V solves this problem. However, it does lead to less efficient two-stage power conversion. The intermediate voltage (48 V) was picked because it is in the proper range and because it is an emerging commercial standard used by the telephone industry and others.

In the near term, very small 48 V to consumption voltage power converters for SEM-E modules are not available. However, both the AF and Navy have at various times had programs to further development in this area. Because of this, in the near term, it may be necessary for JAST backplanes to be flexible enough to accept 3.3 V, 5 V and ±15 V as well as 48 V. Modules should have pins reserved on them for these voltages. IEEE 896.5, Standard for Futurebus+, Profile M (Military), Section 6.4.1 Profile Power will act as the guiding document for the JAST backplane power distribution system. However, power and ground pin assignments for the JAST unified network will be made after interconnect trades are performed.

## 3.5 Module Cooling

| Standard:          | Module Cooling                                                                        |

|--------------------|---------------------------------------------------------------------------------------|

| Goal:              | To establish a mthodology for the avionics modules which ensures adequate reliability |

|                    | of all on-module components                                                           |

| Leading Candidate: | F-22 Liquid Flow Thru Cooling (F-22 Common Module Specification 5PTA3242) for         |

|                    | mission avionics                                                                      |

|                    | F-22 Conduction cooled for the VMS system                                             |

| Other Candidates:  | Conduction cooled, Air flow through cooled, Convection cooled                         |

| Decision Date:     | March 1997                                                                            |

The preferred cooling concept for mission avionics is liquid-flow-through (LFT) cooling using polyalphaolefin (PAO) as the coolant. LFT has the advantage that it can cool a several-hundred watt module while maintaining even temperature across all ICs on the module. Hot spots are well controlled. LFT allows very high density packaging which in turn reduces the overall weight and size of the airplane. In addition, it keeps the overall module cooler. This decreases module failure rate and increases overall reliability. Another advantage of

LFT is that it may make the use of commercial ICs on military modules more viable by keeping temperature within the 70C ambient specified for those ICs.

The main arguments against LFT are that liquid systems require special maintenance, that PAO spilled on a Navy carrier deck could be hazardous, and that LFT is outside the mainstream of commercial technology and hence expensive.

Other candidate cooling methods are conduction cooling, air flow through cooling, and direct impingement convection cooling. Conduction cooling can handle a maximum load of approximately 50 watts. Air flow through cooling, where air is blown through plenums in the metal core of the module, has a capacity of approximately 90 watts. Convection cooling, where air is blown between modules and directly onto ICs, has a capacity of approximately 100 watts, but is very configuration dependent. It also has the disadvantage that outside air, which may contain corrosive pollutants, is blown directly on the ICs and may reduce reliability. None of the alternative candidates provide the amount of cooling which is provided by LFT.

The preferred cooling concept for the VMS system is conduction cooling. Using conduction cooled modules and an air cooled rack makes the VMS independent of any failures in the liquid cooling system. In addition, VMS modules are generally low performance and have low heat loads. However, it is possible to use dual redundant liquid cooling systems to increase the reliability of LFT. The inherent reliability of conduction cooled boards in an air cooled rack, and F-22 compatibility, were the main reasons for choosing conduction cooling for the VMS system.

#### 3.6 Module Form Factor, Mechanical, and Connector

| Standard:          | Module Form Factor                                                             |

|--------------------|--------------------------------------------------------------------------------|

| Goal:              | To establish a unified modular form factor which meets fighter weight, volume, |

|                    | and environmental requirements and is economical to produce.                   |

| Leading Candidate: | F-22 SEM-E module                                                              |

| Other Candidates:  | VME 6U specification, IEEE 896.5 module size 10SU, new form factor             |

|                    | designed for ease of manufacture                                               |

| Decision Date:     | March 1997                                                                     |

The F-22 form factor, mechanical interface, and connector were selected as the JAST preferred concept. The F-22 mission avionics uses a version of the SEM-E format. It is double sided and approximately 6"x6". The basic pitch is .6", although some modules are multiples of the .6" pitch. The connector is the Bendix bristle brush which in its basic format has 360 contacts. There are several versions of the connector for use with coax, fiber optics, and on the power supply modules.

The leading candidate for the Vehicle Management System (VMS) is also a version of the SEM-E. It also uses the Bendix connector. However, it is conduction cooled to the card edge for use in air cooled racks.

The rationale for choosing the F-22 SEM-E module format for the mission avionics was primarily to limit the proliferation of different types of liquid flow through (LFT) formats in the DoD. At this time the F-22 LFT format is the dominant form factor. A few other LFT modules have been developed, but the volume of them is far smaller than the volume of the F-22 modules. Moreover, an IEEE standard (P1101.9) is being developed that which is compatible with the F-22 module. The Bendix connector was chosen for the same reason--namely it is the dominant connector being used on LFT modules at this time. The VMS modules are conduction cooled to air cooled racks because they are required to function even if the liquid cooling system fails. Being in air cooled racks, they are not dependent on the liquid cooling system.

Further trades will be performed to determine the optimum blend of COTS, affordability, and reliability. Technical issues to be investigated include connector, space and height for on-module DC to DC converters, commercial MCM compatibility, and I/O.

Arguments for other form factors include:

- 1) A larger board size would reduce cost because fewer boards would be needed. Less total "housekeeping" and interconnect circuitry would be needed for the total aircraft, since the "housekeeping" and interconnect circuitry is needed only on a per board basis.

- 2) The VME form factor should be considered because it is widely used and cheaper than the SEM-E form factor. It also has the advantage of being larger.

- 3) A new form factor should be designed which allows for ease of manufacture. This new form factor would be designed specifically for production on commercial manufacturing lines such as those used in the automotive industry.

## 3.7 Advanced Stores Management/Weapon System Interface

| Standard:          | Weapons System Interface                                                           |

|--------------------|------------------------------------------------------------------------------------|

| Goal:              | To have an aircraft to weapon system interface standard which will be used by most |

|                    | future weapons in 2000 time frame.                                                 |

| Leading Candidate: | Mil 1760 Weapon Bus                                                                |

| Other Candidates:  | Unified avionics network as a high speed addition to 1760, custom interconnects    |

| Decision Date:     | March 1996                                                                         |

The JAST weapons interface is proposed to be the F-22 Stores Management System (SMS) as implemented by MIL-STD-1760, Class II (except for Type B signals) with the possible enhancement of a higher speed channel. The functions performed by the SMS are: (1) store inventory, (2) missile monitor and control, (3) gun control, (4) expendable countermeasures (EXCM), (5) weapon bay door and launcher control, (6) selective and emergency jettison, and (7) BIT.

The JAST program is examining technology for carrying stores externally which will affect the weapons interface. These stores may include smart weapons with high-data-rate sensors or mission reconfigurable pods--also potentially carrying high-data-rate sensors. Of particular interest are those involving Global Positioning System (GPS) interfaces, video, and ATR processing. To accommodate these it may be necessary to augment the weapons system interface with a higher speed data link. If this is necessary, it is proposed to extend the unified avionics interconnect into the weapons system interface.

#### 3.8 Advanced System Instrumentation and Software Debug Facility

| Standard:          | System Instrumentation and Software Debug Facility                            |

|--------------------|-------------------------------------------------------------------------------|

| Goal:              | To establish a highly capable standard instrumentation and debug capability   |

|                    | across all avionics.                                                          |

| Leading Candidate: | IEEE 896.5, Standard for Futurebus+, Profile M (Military), Annex A1, Software |

|                    | Development Unit.                                                             |

| Other Candidates:  | F-22 system instrumentation and software debug facility                       |

| Decisions:         |                                                                               |

As avionics architectures become more extensive and critical events affecting system behavior become separated by sub-microsecond times, the difficulty of integrating and maintaining the system is also increased in required sophistication. Various techniques, including real time non-intrusive (RTNI) monitoring have been developed to address these needs at the level of <u>individual</u> processors. However, it has been much more difficult to implement RTNI monitoring across an entire aircraft avionics system consisting of <u>many</u> processors. This section addresses the strategy to assure that all aspects of system monitoring, debug, and management remain within manageable bounds for the entire architecture.

The F-22 debug and instrumentation facility was the starting point for the JAST debug and instrumentation facility. However, additional features were deemed necessary for JAST. The following two paragraphs describe the F-22 features. These features were included as proposed functionality for JAST, not as a proposed implementation basis.

The F-22 Common Integrated Processor (CIP) architecture, hardware and software, provide the capability for the following debug and instrumentation functionality. The CIP provides two types of debug capability: low intrusive and intrusive (full debug capability). Both capabilities communicate with the VAX through the DRQ3B (DEC bus) and the CIP TM Bus (JIAWG standard bus for test and maintenance). These debug capabilities provide the application developers the capability to set breakpoints, halt processing, dump registers and memory, etc. The difference between intrusive and low intrusive debug is the type of debug commands provided to the developer (i.e. low intrusive debug allows instruction trace, low intrusive traps causes action, i.e. stop or dump register/memory (small)), while intrusive allows breakpoints, dumping of memory, etc.). The low intrusive debug function is supported only by the software in the operating system, while the intrusive debug function is supported by the software in the operating system and a separate software item, Debug Support Program (DSP). The debugging is used only during laboratory operations, not flight testing (normal operation).

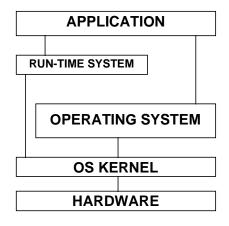

The CIP also provides instrumentation for operation in the laboratory and flight test. This capability is provided with the aid of hardware and software components. The software components are the Simulation, Instrumentation and Debug Support (SIDS) and Data Pump (part of UFO (Utilities for Operational Flight Programs)). The SIDS software is located in the User Console Interface (UCIF) Module, while the Data Pump software is linked with each application that requires data to be pumped. The SIDS software commands the data pump software over the PI-Bus when to pump data (activation table) and what data to pump (definition table). These tables are built by the application developers before flight or laboratory run. The data is pumped across the PI-Bus and onto the fiber optic bus to the Data Acquisition Unit (DAU).